This circuit requires prerequisite knowledge of exor gate binary addition and subtraction full adder.

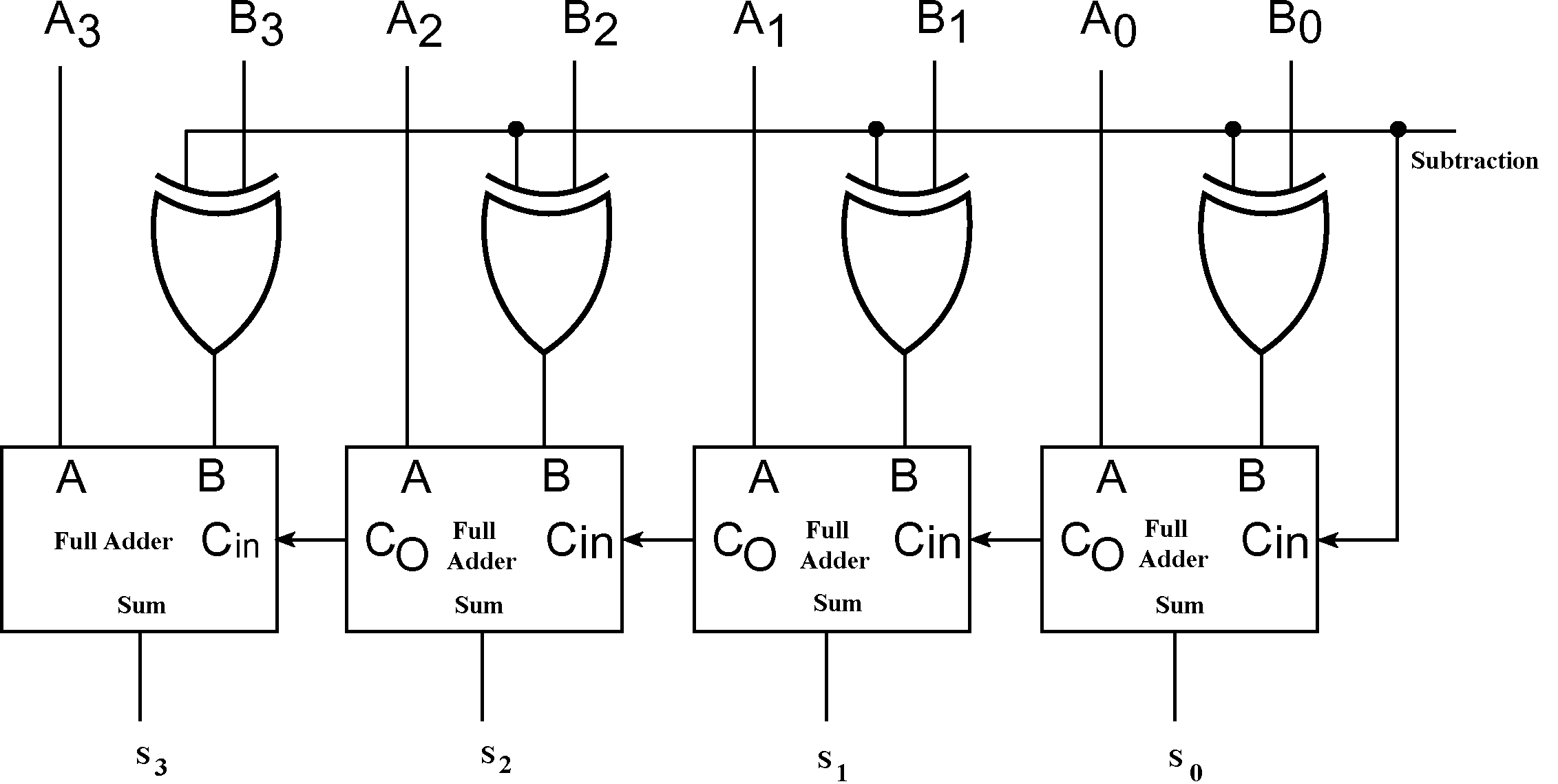

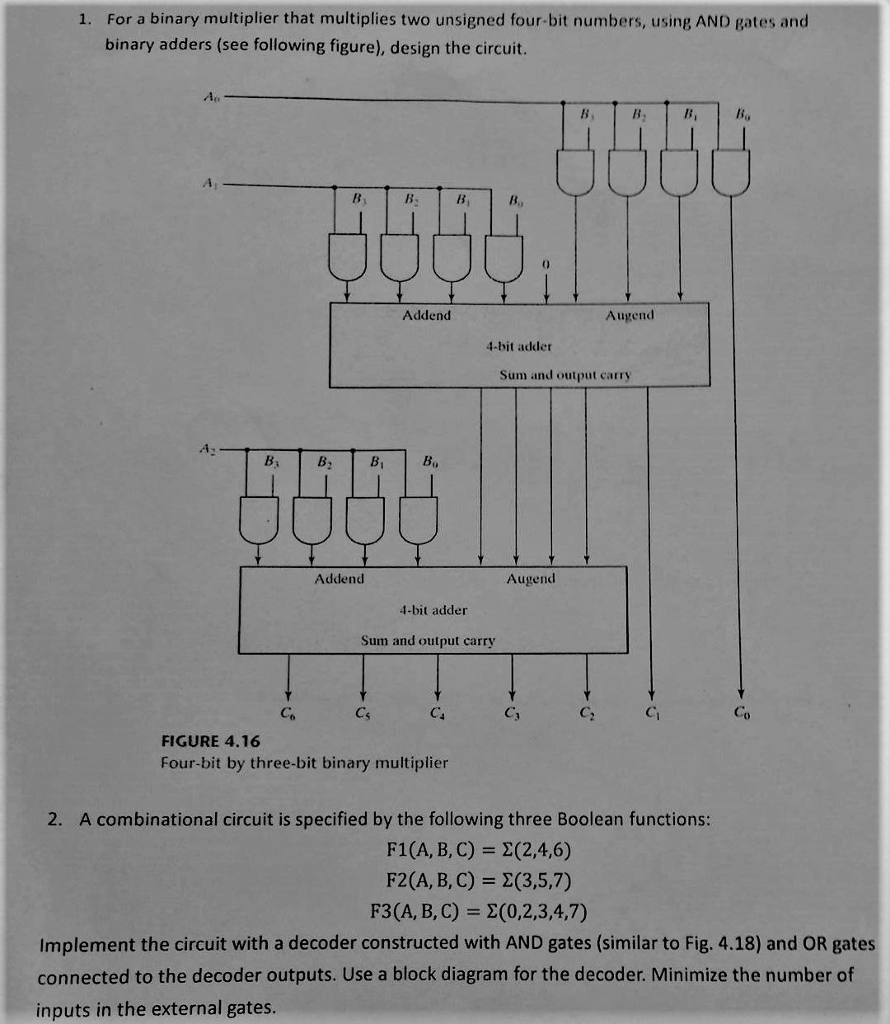

Design a combinational circuit for 4 bit binary subtractor.

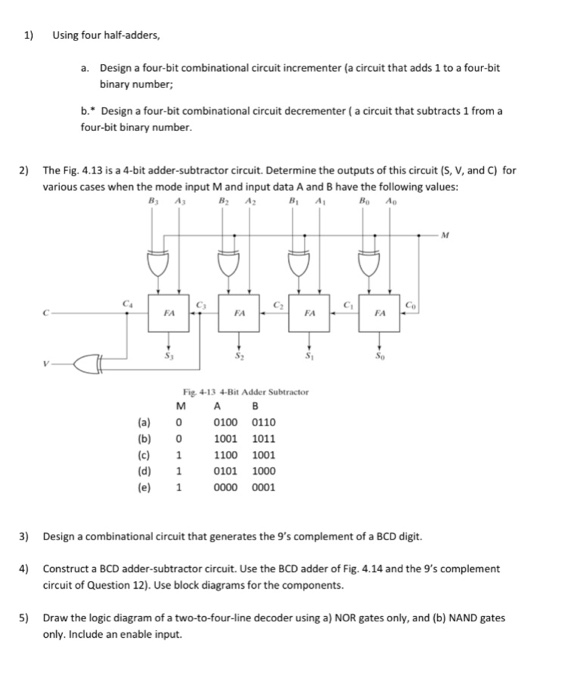

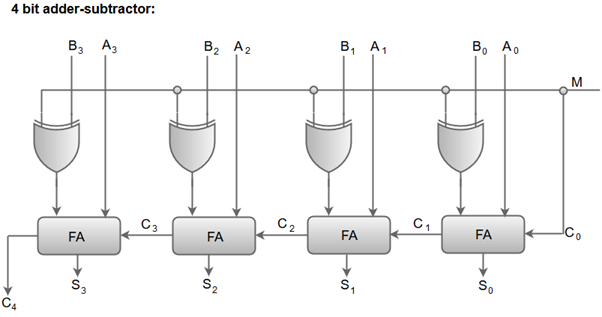

The circuit has a mode input bit m that controls its operation.

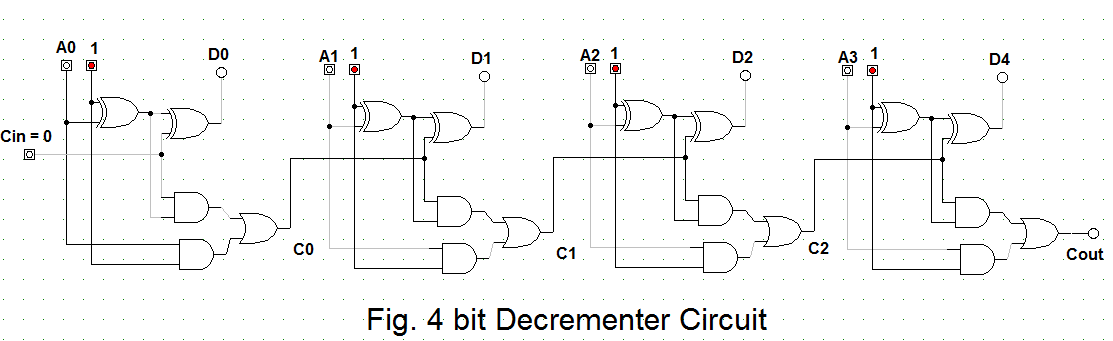

A combinational logic circuit performs a subtraction between the two binary bits by considering borrow of the lower significant stage is called as the full subtractor.

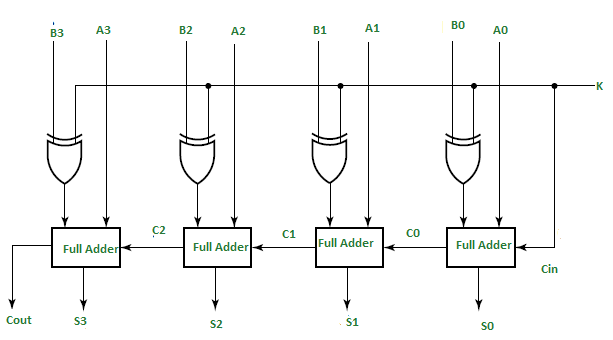

Design a 4 bit adder subtractor circuit using the 4 bit binary full adders 74ls83 and any necessary additional logic gates.

The control input is controls the addition or subtraction operation.

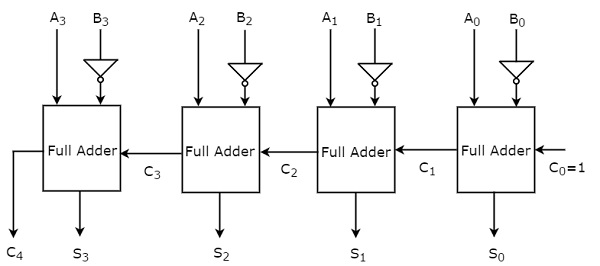

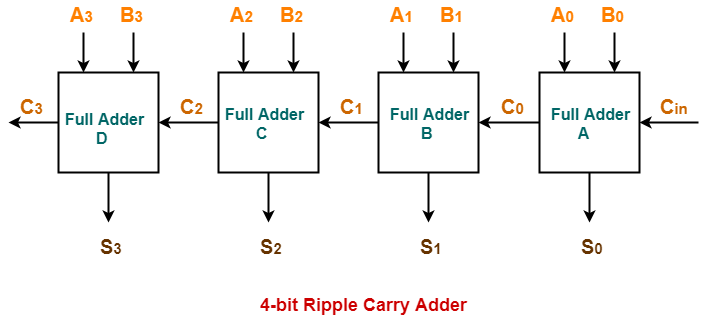

The circuit consists of 4 full adders since we are performing operation on 4 bit numbers.

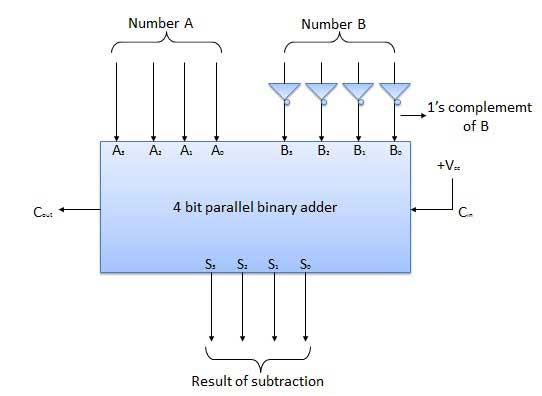

You may use one s or two s compliment of b to perform subtraction.

A0 a1 a2 a3 for a b0 b1 b2 b3 for b.

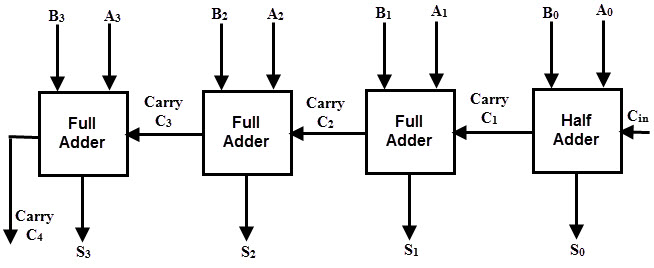

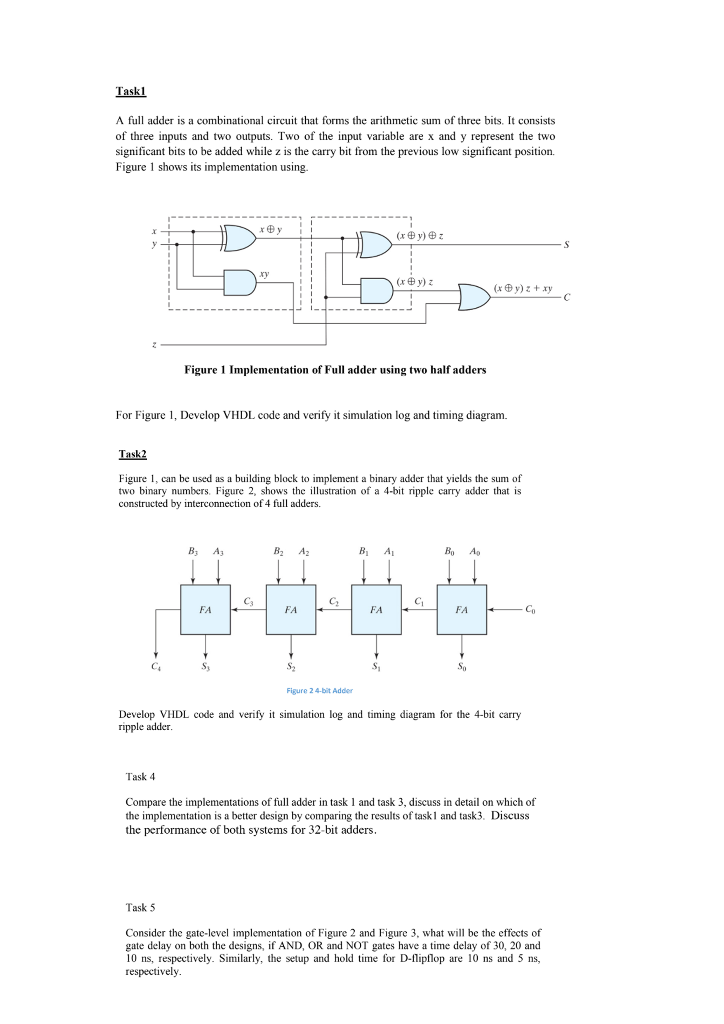

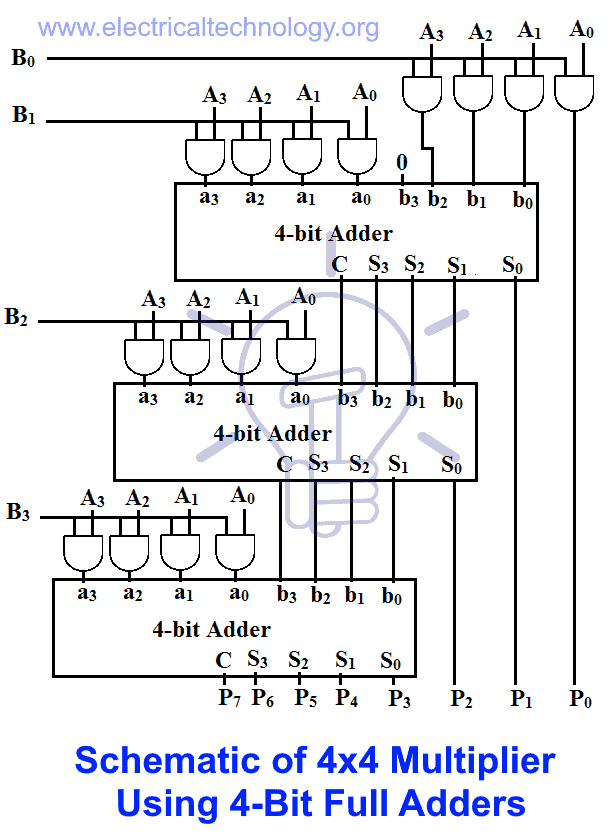

A parallel adder adds corresponding bits simultaneously using full adders.

Specifically when m 0 the circuit becomes a 4 bit adder and when m 1 the circuit becomes a 4 bit subtractor that performs the operation a plus the 2 s complement.

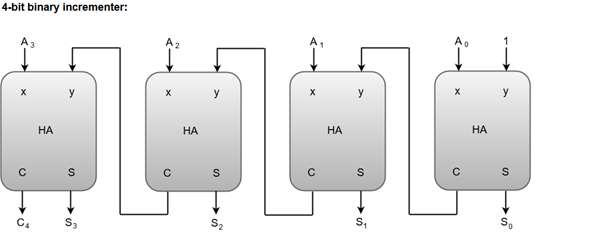

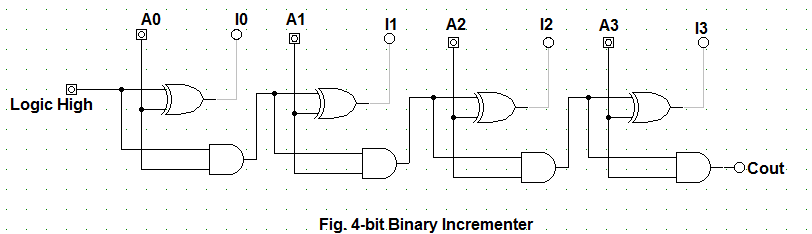

A full adder adds two 1 bits and a carry to give an output.

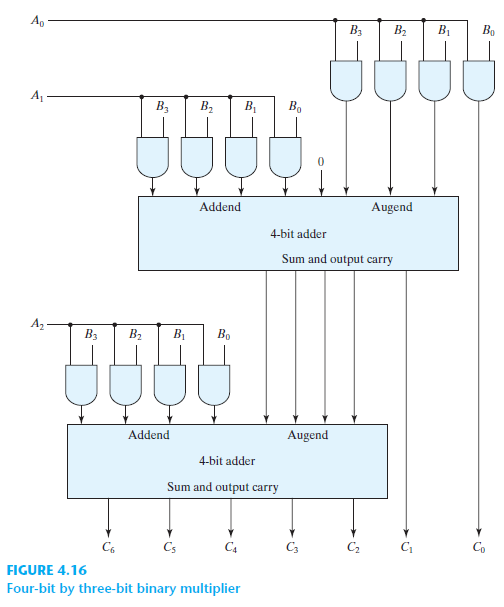

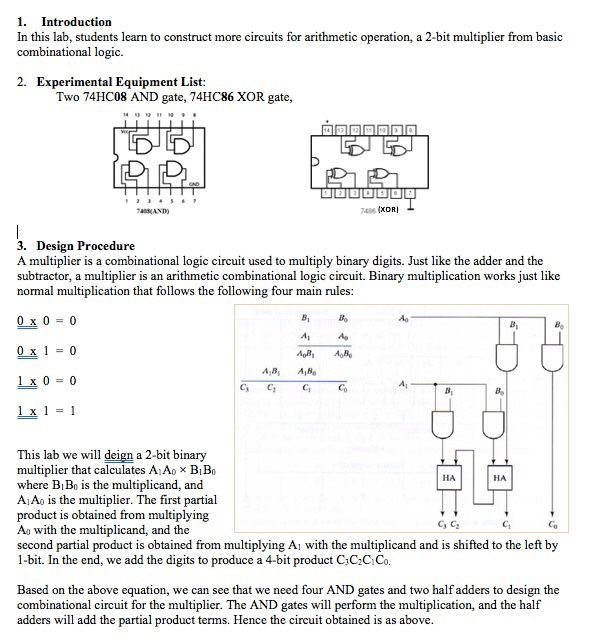

Figure above the realization of 4 bit adder subtractor.

Half subtractor is used to perform two binary digits subtraction.

When the subtraction input is logic 0 the b3 b2 b1 b0 are passed to the full adders.

Given two 4 bit positive binary numbers a and b you are to design an adder subtractor circuit to compute a b or a b depending upon a mode input which controls the operation.

In this subtraction of the two digits is performed by taking into consideration whether a 1 has already borrowed by the previous adjacent lower minuend bit or not.

Lets consider two 4 bit binary numbers a and b as inputs to the digital circuit for the operation with digits.

A parallel adder is an arithmetic combinational logic circuit that is used to add more than one bit of data simultaneously.

From the figure it can be seen that the bits of the binary numbers are given to full adder through the xor gates.

The result with the proper sign is to be displayed in un complemented binary form.

However to add more than one bit of data in length a parallel adder is used.